به نظر میرسد AMD در ریزمعماری نسل بعدی Zen 6 در حال کنار گذاشتن لینکهای SERDES برای ارتباط بین تراشهای (D2D Interconnect) است و به سراغ یک طراحی موازی و عریض موسوم به Sea-of-Wires میرود. این تغییر با مزایای بزرگی چون افزایش پهنای باند و کاهش تاخیر همراه است. جزئیات جالب را در ادامه خبر بخوانید.

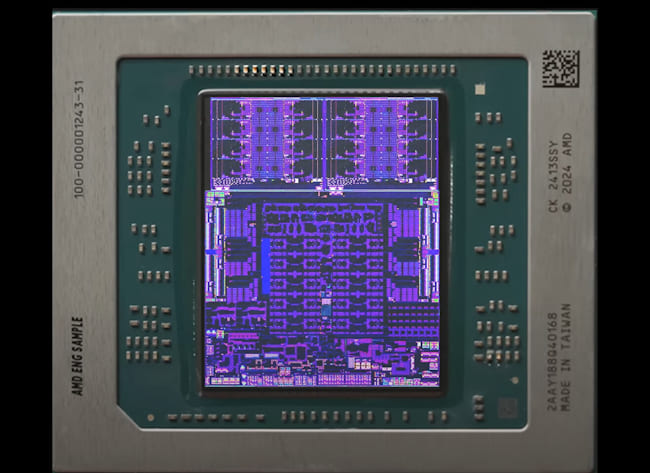

بر اساس گزارش کانال High Yield، این تغییر نخستین بار در تصاویر منتشرشده از نمونههای APU استریکس هیلو (Strix Halo) دیده شده است. در این تصاویر شماتیک بلوک بزرگ SERDES که همیشه در لبه CCDها قرار داشت، دیگر وجود ندارد.

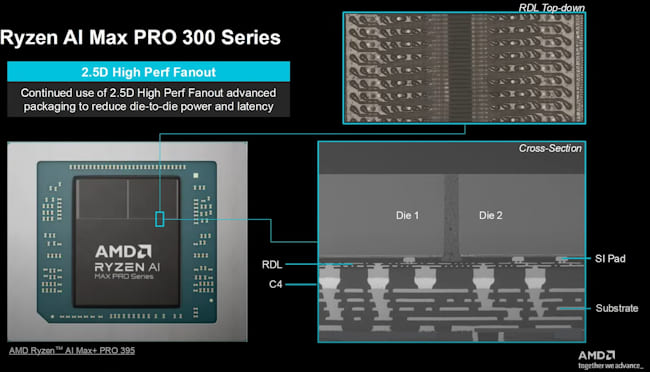

افزون بر ناپدید شدن بلوک SERDES در ریزمعماری Zen 6، نشانههایی از استفاده AMD از فناوری TSMC InFO-oS هم دیده میشود. همه اینها تأیید میکند که تیم قرمز حالا به سراغ مسیرهای موازی متراکم رفته تا سرعت ارتباطات بین دایهای تشکیل دهنده پردازنده را بالا ببرد.

دریایی از مسیرهای ارتباطی

در طراحی فعلی SERDES باید دادهها پیش از ورود یا خروج از هر Die مورد عملیات قرار بگیرند که موجب افزایش تاخیر و مصرف انرژی میشود. در مقابل طراحی Sea-of-Wires با استفاده از مسیرهای کوتاه اما پر تعداد (موازی)، این سربار را حذف میکند و در نتیجه آن میتوان انتظار کاهش مصرف انرژی و تاخیر ارتباطی و افزایش پهنای باند را داشت.

همچنین این کار به کوچکتر شدن اندازه دایها یا استفاده از فضای خالی شده برای ساخت اجزای مفید کمک میکند.

این یعنی در ریزمعماری جدید Zen 6 میتوان انتظار بهبود کارایی به ازای هر وات انرژی مصرفی و همچنین کاهش محسوس تأخیر در پردازشها را داشت. حتی کنترلر حافظه داخلی (IMC) هم از این تغییر سود خواهد برد و دسترسی سریعتری به حافظه رم فراهم میشود.

البته این رویکرد بیدردسر هم نیست. تراکم بالای مسیرهای موازی زیر دای، چالشهایی از نظر افت قدرت سیگنال، دفع گرما، طراحی مسیرهای ارتباطی و تولید انبوه ایجاد میکند. بنابراین AMD برای غلبه بر این مسائل نیازمند طراحی چندلایه و همکاری نزدیک بین تیمهای طراحی تراشه و پکیجینگ خواهد بود.

اگر AMD موفق شود این موانع را پشت سر بگذارد، Zen 6 میتواند نقطه عطفی در ریزمعماریهای مولتی دای باشد و تاخیر را به طرز چشمگیری کاهش دهد.

نظر خود را اضافه کنید.

برای ارسال نظر وارد شوید

ارسال نظر بدون عضویت در سایت