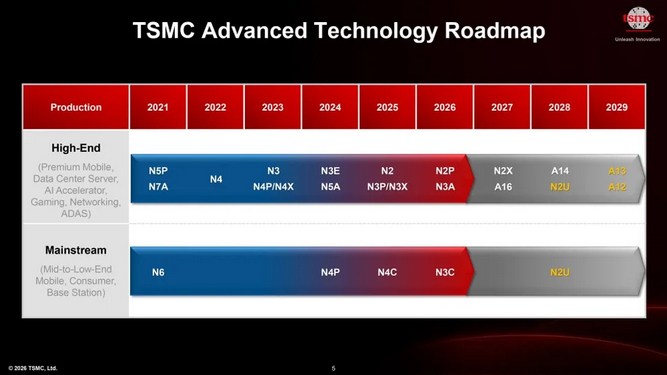

شرکت TSMC در تازهترین نقشه راه خود، تصویری دقیقتر و البته معنادارتر از آینده صنعت نیمههادی ترسیم کرده؛ مسیری که نشان میدهد رقابت در گرههای ساخت، دیگر صرفاً بر سر «کوچکتر شدن» نیست، بلکه بیش از هر زمان دیگری به بهینهسازی هدفمند برای کاربردهای متفاوت گره خورده است. معرفی A12 و A13، اضافه شدن N2U به خانواده ۲ نانومتری و در عین حال کنار گذاشتن High-NA EUV تا پایان دهه، همگی نشانههایی از یک تغییر رویکرد حسابشده هستند.

این شرکت در جریان سمپوزیوم فناوری آمریکای شمالی ۲۰۲۶، جزئیات برنامههای خود تا سال ۲۰۲۹ را منتشر کرد. در این میان، معرفی فناوریهای کلاس ۱.۲ و ۱.۳ نانومتری با نامهای A12 و A13، گسترش غیرمنتظره پلتفرم N2 با نسخه N2U و تأکید بر عدم استفاده از لیتوگرافی EUV با عدد گشودگی بالا (High-NA) از مهمترین نکات بودند. با این حال، آنچه بیش از همه جلب توجه میکند، تثبیت یک استراتژی چندمسیره برای توسعه نسلهای جدید است.

کوین ژانگ، معاون ارشد توسعه کسبوکار و فروش جهانی TSMC، در توضیح این مسیر میگوید:

سال گذشته فناوری A14 را بهعنوان پیشرفتهترین نسل مبتنی بر ترانزیستورهای نانوشیتی با ساختار گیت-همهجانبه (GAA) معرفی کردیم که برای تولید در سال ۲۰۲۸ برنامهریزی شده است.

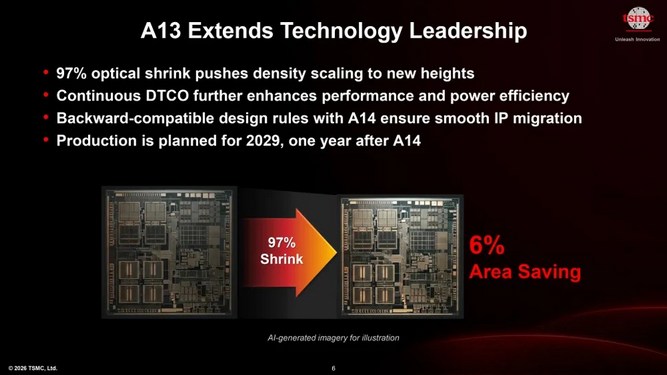

ژانگ به این نکته ظریف اشاره میکند که این شرکت امسال نسخههای مشتقشده از A14 شامل A13 و A12 را معرفی خواهد کرد که هر دو در سال ۲۰۲۹ به تولید میرسند. این مسئول TSMC در خصوص دو فناوری مذکور اضافه میکند که گره A13 در واقع یک بهبود تدریجی مبتنی بر کوچکسازی اپتیکی است.

این فناوری با حفظ کامل سازگاری با قوانین طراحی و ویژگیهای الکتریکی نسل قبل خود، حدود ۶ درصد کاهش مساحت را به همراه دارد. این یعنی مشتریان میتوانند بدون نیاز به بازطراحی گسترده، از مزایای آن بهرهمند شوند.

وقتی یک نسخه برای همه کافی نیست

اگر تا چند سال پیش بازار گوشیهای هوشمند موتور اصلی درآمد TSMC بود، حالا شرایط تغییر کرده است. رشد انفجاری حوزههای هوش مصنوعی و پردازشهای سنگین (HPC) باعث شده نیازها بهشدت متنوعتر شوند؛ موضوعی که مستقیماً در نقشه راه جدید این شرکت بازتاب پیدا کرده است.

TSMC در این مسیر، عملاً از مدل «یک فناوری برای همه کاربردها» فاصله گرفته و به سراغ تفکیک هدفمند گرهها رفته است. در این شرایط با دو ساختار مجزا روبرو خواهیم بود:

- برای دستگاههای مصرفی و کلاینت (مثل گوشی و لپتاپ)، هر سال یک گره جدید ارائه میشود؛ جایی که هزینه، مصرف انرژی و امکان استفاده مجدد از IP اهمیت بالایی دارد.

- برای کاربردهای سنگین مانند دیتاسنترها، AI و HPC، چرخه معرفی به دو سال افزایش یافته تا هر نسل، جهش محسوسی در کارایی ارائه دهد.

در این استراتژی گرههایی مانند N2، N2P، N2U، A14 و A13 بیشتر مناسب کاربردهای کلاینت هستند؛ در این گروه، بهبودهای تدریجی اما کمهزینه، منطقیتر از جهشهای بزرگ و پرریسک است.

در مقابل، فناوریهایی مانند A16 و A12 برای بارهای کاری سنگین طراحی شدهاند که در آنها افزایش واقعی کارایی، حتی به قیمت هزینه بالاتر، یک ضرورت محسوب میشود.

A13 و N2U؛ بهبودهای هوشمند بدون دردسر طراحی

فناوری A14 که سال گذشته معرفی شد، قرار است در سال ۲۰۲۸ بهعنوان گره پرچمدار برای محصولات ردهبالای کلاینت وارد خط تولید شود. این فناوری با تکیه بر نسل دوم ترانزیستورهای GAA و فناوری NanoFlex Pro، امکان بهینهسازی دقیقتر طراحی را فراهم میکند.

در ادامه همین مسیر، A13 بهعنوان نسخه تکاملیافته A14 معرفی شده است. TSMC در توضیحات خود میگوید که A13 نه با یک جهش بزرگ، بلکه با رویکردی آشنا و کاربردی که کوچکسازی اپتیکی (Optical Shrink) همراه شده که در آن ابعاد خطی طرح حدود ۳ درصد کاهش پیدا میکند، چگالی ترانزیستور تقریباً ۶ درصد افزایش مییابد و مهمتر از همه، سازگاری کامل با طراحیهای قبلی حفظ میشود.

از دید فنی این همان مسیری است که پیشتر در گرههایی مانند N6، N4 و N3P هم دیده بودیم. همانطور که بالاتر نیز اشاره شد، در این تکنیک، شرکتها میتوانند با حداقل تغییر و بدون آنکه وارد چرخه پرهزینه بازطراحی کامل شوند، محصولات بهینهتری تولید کنند.

در مقابل، A14 برای دستیابی به حداکثر بهبود در مصرف توان، کارایی و تراکم ترانزیستورها، نیازمند استفاده از ابزارها و متدولوژیهای طراحی کاملاً جدید است. اما A13 با تکیه بر بهینهسازی مشترک طراحی و فناوری (DTCO)، این بهبودها را بدون چنین الزامی ارائه میدهد. طبق اعلام شرکت تایوانی، تولید انبوه A14 برای سال ۲۰۲۹ در نظر گرفته شده است.

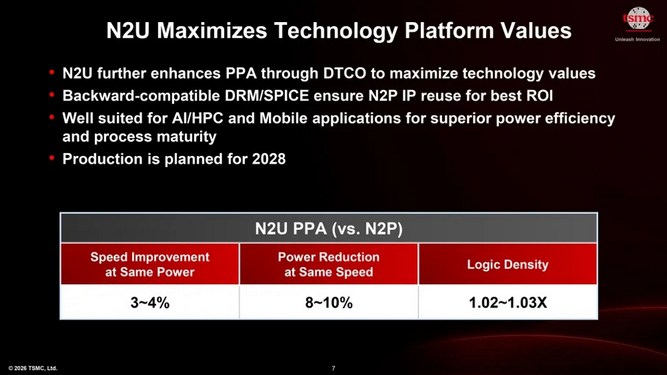

در کنار آن، N2U بهعنوان یک گزینه اقتصادیتر برای ارتقای طراحیهای مبتنی بر N2 معرفی شده است. این گره که ادامه تکامل پلتفرم ۲ نانومتری محسوب میشود، ۳ تا ۴ درصد کارایی بیشتر در همان مصرف انرژی ارائه میدهد. در عین حا مصرف انرژی یک سطح کارایی یکسان در نسل جدید، بین ۸ تا ۱۰ درصد پایینتر بوده و استفاده از آن موجب بهبود جزئی ۲ تا ۳ درصدی در چگالی منطقی تراشه میگردد.

نکته کلیدی اینجاست که N2U با IPهای مبتنی بر N2P کاملاً سازگار است. این یعنی در عمل، شرکتها میتوانند بدون مهاجرت به یک گره کاملاً جدید، محصولات تازهای توسعه داده و هزینههای خود را به شکل محسوسی کاهش دهند.

A16 و A12؛ جایی که کارایی حرف اول را میزند

در سوی دیگر این نقشه راه، فناوریهایی قرار دارند که برای کاربردهای سنگین طراحی شدهاند. A16 یکی از مهمترین این تکنیکهاست که با استفاده از فناوری تأمین توان از پشت ویفر (Backside Power Delivery) با نام Super Power Rail، مستقیماً محدودیتهای توان و جریان در پردازشهای سنگین را هدف قرار میدهد.

A16 در واقع نسخهای از N2P بههمراه این فناوری جدید است که با وجود استفاده از نسل اول ترانزیستورهای GAA و البته با هزینه بالاتر، بهبود محسوسی در کارایی، مصرف انرژی و چگالی ترانزیستور ارائه میدهد.

البته TSMC اشاره کرده که زمانبندی عرضه این فناوری به سال ۲۰۲۷ منتقل شده است. ژانگ در اینباره توضیح میدهد:

A16 از نظر فنی در سال ۲۰۲۶ آماده خواهد بود، اما زمان شروع تولید انبوه به برنامه مشتریان بستگی دارد و انتظار داریم در سال ۲۰۲۷ به مقیاس بالا برسد.

در همین حال، N2X همچنان در سبد محصولات شرکت باقی میماند؛ این نسخه گره بسیار جذابی است که به عنوان نسخه بهینهشده از N2P، با استفاده از تأمین توان از سمت جلوی ویفر، امکان دستیابی به فرکانسهای بالاتر را فراهم میکند.

اما در این زمینه باید فناوری هیجانانگیز A12 را در نظر داشته باشیم. این گره برای سال ۲۰۲۹ برنامهریزی شده و قرار است جهشی کامل در سطح یک نسل جدید ارائه دهد. فناوری ساخت A12 احتمالاً با تکیه بر نسل دوم ترانزیستورهای GAA و NanoFlex Pro، همان نقشی را ایفا میکند که A14 برای N2 داشت.

ژانگ در این خصوص میگوید:

A16 نخستین نسل ما با Super Power Rail است و A12 نسل بعدی آن خواهد بود. A13 و A12 بر پایه A14 و با کوچکسازی قابلتوجه هندسی توسعه یافتهاند. برای دستیابی به چگالی بالاتر، باید هم در سمت جلویی و هم در سمت پشتی ویفر مقیاسپذیری انجام شود. به همین دلیل، در مسیر A16 تا A12 بهبودهای متعددی، بهویژه در بخش تأمین توان از پشت ویفر، اعمال خواهد شد.

فعلاً خبری از High-NA EUV نیست

در انتها باید به این نکته مهم اشاره کنیم که نقشه راه شرکت تایوانی با یک شگفتانه (شاید نهچندان جذاب) همراه شده است. یکی از تصمیمات قابلتوجه TSMC این است که حداقل تا سال ۲۰۲۹، برنامهای برای استفاده از لیتوگرافی High-NA EUV در شرکت در نظر گرفته نشده است. این موضوع نشان میدهد که شرکت تایوانی، مسیری متفاوت از Intel را در نظر گرفته که پیش از این اعلام کرده بود قصد دارد از این فناوری در گره 14A و نسلهای بعدی خود استفاده کند.

ژانگ در اینباره میگوید:

باید بگویم از تیم تحقیق و توسعهمان شگفتزدهام. آنها همچنان راههایی برای ادامه مقیاسپذیری بدون نیاز به High-NA پیدا میکنند. شاید در آینده به آن نیاز داشته باشیم، اما در حال حاضر میتوانیم از EUV فعلی بیشترین بهره را ببریم و سراغ گزینهای که بسیار پرهزینه است، نرویم.

نظر خود را اضافه کنید.

برای ارسال نظر وارد شوید

ارسال نظر بدون عضویت در سایت