در حالی که تراشههای ساخته شده با فناوری 2 نانومتری هنوز وارد بازار نشدهاند، موسسه مهندسین صنعت نیمههادی کرهجنوبی اعلام کرد که دستیابی به فناوری ساخت 0.2 نانومتری، احتمالاً تا 15 سال دیگر اتفاق بیفتد.

به گزارش وبسایت WCCFTech، در حالی که سامسونگ چندی پیش از اولین تراشه 2 نانومتری دنیا، یعنی اگزینوس 2600 پرده برداشت، موسسه مهندسین صنعت نیمههادی کرهجنوبی در خلال انتشار نقشهراه فناوری نیمههادی سال 2026 اعلام کرد که دستیابی به فناوری ساخت 0.2 نانومتری تا سال 2040 امکانپذیر است.

البته با توجه به مدت طولانی اعلام شده توسط این موسسه و موانع غیرقابل پیشبینی بر سر راه ساخت ویفرهای یک نانومتری، دستیابی به این فناوری در سال 2040، نیاز به پیشرفت بسیار زیادی دارد.

بر اساس گزارشهای منتشر شده، در نقشه راه این موسسه، به 9 فناوری اصلی دیگر نیز اشاره شده که شامل تراشهها و فرآیندهای نیمههادی، نیمههادیهای هوش مصنوعی، نیمههادیهای اتصال نوری، حسگرهای نیمههادی اتصال بیسیم، نیمههادیهای اتصال باسیم، PIM، پکیجینگ و محاسبات کوانتومی میشود.

همچنین این نقشه راه به افزایش تعداد لایههای فلش NAND از 321 به 2000 و انجام چندین تریلیون عملیات در ثانیه توسط نیمههادیهای هوش مصنوعی در آینده نیز اشاره کرده است.

پیشرفت لیتوگرافی و فناوریهای ۲ نانومتری

همانطور که در بالا گفته شد، در حال حاضر کمترین لیتوگرافی متعلق به GAA سامسونگ یعنی 2 نانومتر است، اما گزارشها حاکی از آن است که این شرکت، برنامههایی برای تهیه نسخههای بهتر این فناوری ساخت دارد.

برای مثال، این غول کرهای، طراحی GAA Node نسل دوم فناوری 2 نانومتری را امسال به پایان رسانده و آماده شروع به کار روی SF2P+ یا همان نسل سوم فناوری 2 نانومتری تا 2 سال آینده است.

چشمانداز 2040: تراشههای 0.2 نانومتری

بر اساس برآوردهای انجام شده، تا سال ۲۰۴۰ فرآیند ۰.۲ نانومتری از ساختار ترانزیستوری نسل جدید CFET (ترانزیستور اثر میدان مکمل) و طراحی سهبعدی یکپارچه (Monolithic 3D) بهره خواهد برد.

همچنین سامسونگ سال 2029 را برای ساخت تراشههای یک نانومتری هدفگذاری کرده و حتی تیمی را برای تحقیق روی این فناوری تشکیل داده است.

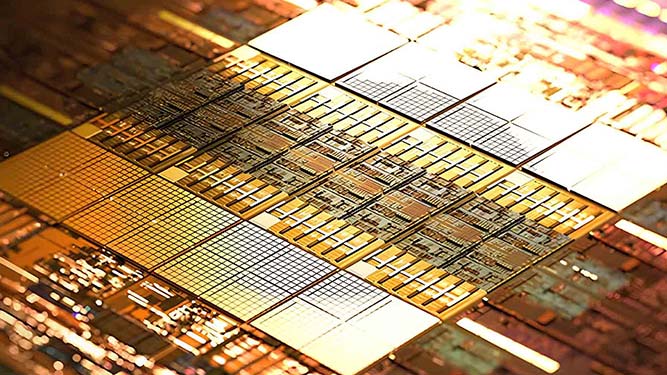

تاثیر روی HBM، DRAM و NAND

به نظر میرسد برنامههای منتشر شده، تنها به تراشههای گوشی محدود نیست و به DRAM و HBM نیز مربوط میشود. بر اساس گزارشهای منتشر شده، مدار حافظههای DRAM از 11 نانومتر به 6 نانومتر کاهش خواهد یافت. همچنین این گزارشها از افزایش لایههای حافظه HBM از 12 به 30 و پهنای باند از 2 ترابایت برثانیه به 128 ترابایت بر ثانیه خبر میدهند.

در بخش NAND نیز، در حالی که SK hynix موفق به توسعهی QLC با ۳۲۱ لایه شده، پیشرفتهای آینده امکان تولید ۲,۰۰۰ لایه QLC را فراهم خواهند کرد.

در همین رابطه بخوانید:

- خیانت میلیارد دلاری؛ دستگیری مدیران سابق سامسونگ به جرم انتقال فناوری ساخت حافظه ۱۰ نانومتری به چین

- نقشه راه AMD برای Zen 6 و Zen 7 رسماً تأیید شد؛ تمرکز ویژه بر هوش مصنوعی

در نهایت، این نقشه راه، در حالی که پردازندههای AI کنونی حدود 10 TOPS توان پردازشی دارند، دستیابی به تراشههایی با قدرت 1000 TOPS برای یادگیری و 100 TOPS برای استنتاج را در سال 2040 پیشبینی کرده است.

نظر خود را اضافه کنید.

برای ارسال نظر وارد شوید

ارسال نظر بدون عضویت در سایت