استاندارد PCI Express در ادامه مسیر تکاملی خود، حالا به نقطهای نزدیک شده که پهنایباندی در مقیاس ۱ ترابایتبرثانیه را هدف گرفته است؛ اما آنچه در ظاهر یک جهش عددی به نظر میرسد، در واقع ورود به مرحلهای جدید از پیچیدگیهای فنی در سطح طراحی سیستم، سیگنالینگ و زیرساخت محسوب میشود. در ادامه با بررسی چالشهای استاندارد PCIe 8.0 همراه ما باشید.

استاندارد PCIe را بیشتر ما با اتصال کارت گرافیک برای دسترسی به سرعت پردازش بیشتر میشناسیم. اما حقیقت این است که این استاندارد، اینروزها مسیری را در پیش گرفته که هر قطعه فوق سریعی را میزبانی کند. درحالیکه هنوز زمان دقیقی برای ورود گسترده دستگاههای بر پایه مانند PCIe 6.0 و PCIe 7.0 در بازار وجود ندارد، زمزمهها در مورد PCIe 8.0 اعدادی فضایی را برای آن نشان میدهند؛ بازتعریف ارتباط مستقیم در کامپیوترها با سرعتی تا 1 ترابایت بر ثانیه!

ادامه سنت «دو برابر شدن»؛ اما با هزینهای بهمراتب بیشتر

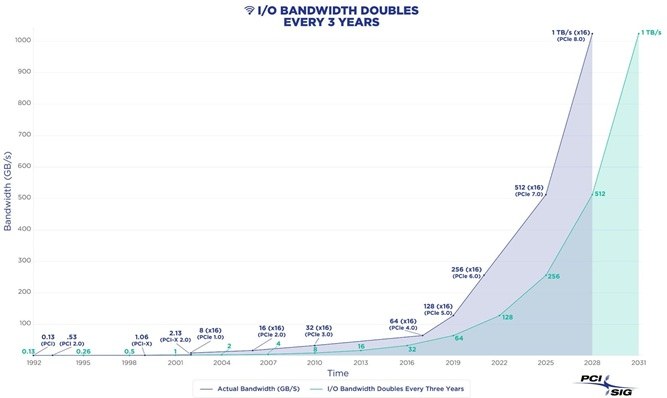

وبسایت Tom’s Hardware در همین زمینه به بررسی ایدهها و به نوعی نقشه راه این استاندارد پرداخته است. این وبسایت در مقاله خود بیان میکند که رویکرد مهندسان انجمن PCI‑SIG بر این است که PCI Express بر همان اصل قدیمی استوار باشد: دو برابر کردن پهنایباند در هر نسل.

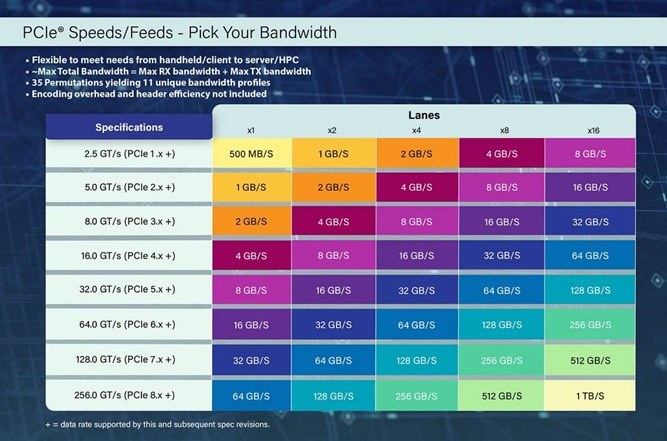

در همین چارچوب، PCIe 8.0 با نرخ ۲۵۶ گیگاترنسفر بر ثانیه در هر لاین تعریف شده و در پیکربندی x16 میتواند به پهنایباند دوطرفهای نزدیک به ۱ ترابایتبرثانیه دست پیدا کند.

این جهش، در نگاه اول ادامهای طبیعی از مسیر PCIe 5.0 و PCIe 6.0 به نظر میرسد، اما واقعیت این است که هرچه سرعت بالاتر میرود، هزینه دستیابی به این افزایش عملکرد بهصورت نمایی رشد میکند. بهعبارت دیگر، PCIe دیگر صرفاً با بهینهسازیهای تدریجی قابل ارتقا نیست و برای رسیدن به نسلهای جدید، نیاز به تغییرات عمیق در لایه فیزیکی دارد.

در همین زمینه ال یانس (Al Yanes)، رئیس و مدیرعامل PCI-SIG، در زمان معرفی این فناوری گفته بود:

پس از عرضه مشخصات PCIe 7.0 در سال جاری (2025)، هیجانزدهایم که اعلام کنیم مشخصات PCIe 8.0 با دو برابر کردن نرخ داده به ۲۵۶ گیگاترنسفر بر ثانیه، سنت دو برابر کردن پهنای باند هر سه سال یکبار را حفظ میکند. با افزایش نیاز به توان پردازشی داده در هوش مصنوعی و سایر کاربردها، تقاضا برای عملکرد بالا همچنان قوی باقی مانده است.

جایی فراتر از کاربر نهایی؛ تمرکز کامل بر AI و دیتاسنتر

برخلاف نسلهای ابتدایی PCIe که رشد آنها با نیازهای کاربران دسکتاپ و عمدتاً کارت گرافیک هدایت میشد، PCIe 8.0 عملاً محصول دوران هوش مصنوعی و دیتاسنترهاست.

بارهای کاری مدرن (از آموزش مدلهای زبانی بزرگ گرفته تا پردازشهای HPC) نیازمند جابهجایی حجم عظیمی از داده میان CPU، GPU و شتابدهندهها هستند. در چنین شرایطی، گلوگاه اصلی دیگر توان پردازشی نیست، بلکه پهنایباند ارتباطی است. PCIe 8.0 دقیقاً برای رفع همین گلوگاه طراحی شده و نقش آن بیش از هر چیز در زیرساختهای ابری و خوشههای محاسباتی تعریف میشود.

این در حالی است که در بازار مصرفی، حتی PCIe 5.0 نیز هنوز بهطور کامل به اشباع نرسیده و فاصله قابلتوجهی میان نیاز واقعی کاربران و ظرفیت استانداردهای جدید وجود دارد.

مرزهای علوم مواد و فیزیک؛ جایی که مس دیگر پاسخگو نیست

چالش اصلی PCIe 8.0 نه در طراحی منطقی، بلکه در محدودیتهای فیزیکی نهفته است. با افزایش نرخ انتقال به ۲۵۶ GT/s، انتقال سیگنال روی مسیرهای مسی با مشکلات جدی مواجه میشود؛ از افت سیگنال گرفته تا افزایش نویز و محدود شدن طول مسیرها روی برد.

در این سطح از سرعت، حتی طراحی PCB به یک مسئله پیچیده مهندسی تبدیل میشود و استفاده از Retimerها و تقویتکنندههای سیگنال به یک الزام بدل میشود، نه انتخاب. همین موضوع هزینه و مصرف انرژی را بهطور قابل توجهی افزایش میدهد. برای توضیح بیشتر باید بگوییم که Retimer در ارتباطات یک دستگاه یا مدار میکروالکترونیکی است که سیگنال دیجیتال با سرعت بالا را بازسازی و دوباره میفرستد تا زمانبندی، سطح سیگنال و کیفیت انتقال در مسیر طولانیتر حفظ شود.

در نتیجه، بدیهی است که مهندسان اینحوزه بهطور جدی به بررسی جایگزینهایی مانند ارتباطات نوری فکر کنند. این رویکرد میتواند محدودیتهای فیزیکی مس را پشت سر بگذارد، اما خود با چالشهای اقتصادی و مهندسی تازهای همراه میشود.

PAM4؛ راهحل ضروری با پیامدهای اجتنابناپذیر

PCIe از نسل ششم به بعد به سیگنالینگ PAM4 مهاجرت کرده و PCIe 8.0 نیز بر همین اساس توسعه مییابد. این روش با انتقال چند سطحی داده در هر سیکل، امکان افزایش نرخ انتقال را فراهم میکند، اما در مقابل، حاشیه اطمینان سیگنال را کاهش میدهد.

سیگنالینگ PAM4 (Pulse Amplitude Modulation 4‑level) یک تکنیک مدولاسیون است که در هر نماد از چهار سطح مختلف ولتاژ استفاده میکند و در نتیجه هر نماد دو بیت (00، 01، 10، 11) را منتقل میکند. رویکرد مورد استفاده در این تکنیک باعث دو برابر شدن نرخ داده نسبت به مدولاسیون NRZ میشود.

این فناوری برای لینکهای کوتاهفاصله و پهنای باند بالا مانند 100 تا 400 گیگابیت بر ثانیه طراحی شده و نیاز به فیلترها و تشخیص سیگنال دقیقتر دارد، اما بهرهوری نوری بیشتری ارائه میدهد.

نتیجه این وضعیت، افزایش وابستگی به مکانیزمهای تصحیح خطا (FEC) است؛ موضوعی که اگرچه پایداری لینک را حفظ میکند، اما بخشی از پهنایباند مؤثر را کاهش میدهد. بنابراین، فاصله میان سرعت اسمی و عملکرد واقعی، به یکی از چالشهای کلیدی نسلهای جدید PCIe تبدیل شده است.

گلوگاه واقعی: یکپارچهسازی در سطح سیستم

شاید مهمترین تغییر پارادایم در مسیر PCIe، انتقال چالشها از سطح رابط به سطح سیستم باشد. در سرعتهای جدید، هماهنگی میان اجزای مختلف (از پردازنده و حافظه گرفته تا شتابدهندهها) به مراتب پیچیدهتر میشود.

در این میان، استانداردهایی مانند CXL بهعنوان مکمل PCIe اهمیت بیشتری پیدا میکنند، چرا که مدیریت حافظه اشتراکی و انسجام دادهها بدون چنین لایههایی عملاً امکانپذیر نیست. همچنین، مصرف انرژی و مدیریت حرارتی به فاکتورهای تعیینکننده در طراحی پلتفرمها تبدیل شدهاند؛ موضوعی که بهویژه در دیتاسنترها اهمیت حیاتی دارد.

PCIe 8.0 چه زمانی وارد بازار میشود؟

اگرچه استاندارد PCIe 8.0 همین حالا نیز به صورت کامل روی کاغذ تعریف شده، اما فاصله آن تا کاربرد عملی بسیار قابل توجه است. پیشبینیها نشان میدهد که این استاندارد تا اواخر دهه جاری به بلوغ نمیرسد و ورود آن به محصولات مصرفی احتمالاً به دهه آینده و حتی اواسط دهه 2030 میلادی موکول خواهد شد.

تجربه PCIe 6.0 نیز نشان داده که پیچیدگی فنی و هزینه پیادهسازی میتواند روند پذیرش را بهشدت کند کند؛ موضوعی که احتمالاً در مورد PCIe 8.0 با شدت بیشتری تکرار خواهد شد.

جمعبندی

PCIe 8.0 را نمیتوان صرفاً یک ارتقای نسل بعدی دانست؛ این استاندارد نشانهای از ورود صنعت ارتباطات فوق سریع سیمی به مرحلهای است که در آن، افزایش سرعت دیگر یک مسئله خطی نیست، بلکه نیازمند بازتعریف کامل معماری ارتباطات درونسیستمی است.

رسیدن به پهنایباند ۱ ترابایتبرثانیه، اگرچه از نظر فنی ممکن شده، اما تحقق آن در دنیای واقعی، به حل مجموعهای از چالشهای عمیق در حوزه فیزیک، مهندسی و اقتصاد وابسته است؛ چالشهایی که آینده PCI Express را شکل خواهند داد.

![کدام قطعات سختافزاری در بحران زودتر نایاب میشوند؟ [تماشا کنید] راهنمای خرید قطعات سخت افزاری در شرایط بحران](/fa/modules/mod_raxo_related_articles/tools/tb.php?src=%2Ffa%2Fimages%2F1404%2F05%2F02%2FHW-Market-in-War-1-YT-Cover.jpg&w=380&h=213&zc=1)

نظر خود را اضافه کنید.

برای ارسال نظر وارد شوید

ارسال نظر بدون عضویت در سایت